En la siguiente entrada, vamos a realizar un ejercicio

práctico de cómo implementar una máquina de estados tipo Mealy en el CPLD

XC9572.

¿Qué es una máquina de estados tipo Mealy?

Es un tipo de máquina de estados finitos, en la cual las

salidas cambian en función de las entradas.

Ejercicio a implementar:

Se

desea proyectar el gobierno de un conmutador rotativo, que permite realizar un

ciclo completo cuando el tambor

haya

efectuado una vuelta completa.

El

disco solidario del tambor lleva un saliente para actuar sobre el contacto (a).

El

pulsador (b) (botón de impulsos) da comienzo al ciclo.

1)

Estado inicial (reposo) a=1, b=0, M=0.

2)

(b) es accionado y después desaccionado rápidamente (impulso) -> M=1.

3)

Cuando el disco ha dado una vuelta, (a) es accionado por el saliente y

el disco se para.

Vamos

a entender en primer lugar el funcionamiento de la maquina rotativa:

La

máquina está formada por un pulsador de marcha (b), un contacto(a), y un disco

accionado por un motor (m).

En

el momento que pulsamos el botón de marcha (b), se genera un pulso o un cambio

de nivel, que activa el motor (m), produciendo el giro del disco. En el momento

que se activa el contacto(a), el motor se para.

Vamos

a observar ahora la tabla de estados:

Mediante

la tabla de estados, se puede apreciar los estados estables que va a poseer la

máquina.

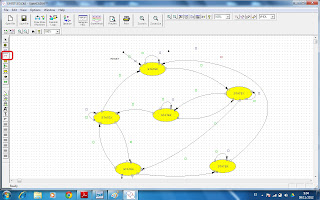

Por

último y para comprender mejor el ejercicio, tenemos el diagrama de flujo, que

nos expresa gráficamente la secuencia del proceso de la máquina rotativa.

Una

vez que tenemos analizado el ejercicio, nos pondremos manos a la obra y

crearemos un proyecto nuevo, que yo he llamado M_ROTATIVA.

Como

en los casos anteriores, tenemos que configurar el CPLD, como la familia,

dispositivo, encapsulado, velocidad…Seleccionaremos los mismos que

anteriormente(deberían estar guardados por defecto).

A

continuación añadiremos una nueva fuente

de tipo esquemático, para poder implementar posteriormente nuestro

diseño. La hemos llamado maq_rota.

Una

vez añadida la fuente de tipo esquemático, añadiremos una nueva fuente de tipo

“State Diagram”.

Xilinx

nos ofrece una herramienta llamada “State Cad”, la cual es un entorno de diseño

gráfico, que nos permite diseñar autómatas de máquinas de estados.

State Cad

Una

vez añadida la fuente tipo “State Diagram”, automáticamente nos cargará el

entorno State Cad, en el cual voy a especificar las funciones principales.

Explicadas

las funciones, nos pondremos manos a la obra e iremos insertando los estados

que dispone nuestra máquina.

Mediante

la opción añadir transición, iremos uniendo las transiciones disponibles entre

estados, analizando claramente la tabla de estados y el diagrama.

A

continuación añadiremos el Reset.

Nos

preguntará si lo queremos en modo asíncrono o síncrono. En nuestro caso será

Asíncrono.

El

siguiente paso será editar las transiciones, para ello simplemente hacemos

doble click en cada una de ellas.

En

el campo condición, definiremos cuáles serán las condiciones de entrada.

Después

hacemos click en “Output Wizard”, y configuraremos las condiciones de salida.

Podemos

configurar las variables, para ello, hacemos click en Options->Variable,

apareciéndonos la siguiente ventana, podremos configurar el tipo, activo,

pin/nodo.

Una

vez acabado este será nuestro resultado final, ahora comprobaremos los estados

y transiciones de que estén bien, para ello haremos utilizaremos la herramienta

“StateBench”.

Al

haber hecho click en “StateBench”, nos ha aparecido abajo las herramientas del

TestBench, con las cuales tenemos dos opciones, podemos hacer la verificación

manualmente por ciclos o que nos haga la verificación de forma automática.

Aquí

se puede observar el resultado al seleccionar “Automatic TestBench”. No

recomiendo hacerlo automático, ya que la mejor forma de comprobar nuestra

máquina de estados es de forma manual por ciclos.

Por

último para finalizar con el programa State Cad, vamos a generar el código

VHDL, haremos click en “Generate HDL”. Aquí se puede ver el resultado de la

compilación, si hubiera algún error nos lo mostraría.

Al

hacer click en “Close”, nos aparecerá el código en VHDL en una ventana, esté

código es el componente en sí, que vamos a insertar en la fuente esquemática.

Guardaremos

el proyecto, y volveremos al entorno de Xilinx, para añadir una fuente

seleccionando, el archivo que hemos generado en StateCad, en este caso le hemos

llamado M_rota.vhd.

Una

vez añadida, en la ventana de procesos, hacemos doble click en “Create

Schematic Symbol”, para que nos genere el componente. Si nos ha completado con

éxito, nos tiene que aparecer en la ventana de abajo que se ha completado con

éxito.

Ahora

ya podemos añadir el componente en la fuente de tipo esquemático.

Creado

el componente, pasaremos a establecer las Marcas I/O, e insertaremos los BUFG y

BUFGSR en Clock y Reset.

Asignación de restricciones

Ahora

pasaremos a crear el fichero de restricciones *.ucf, para ello añadiremos una

nueva fuente, como tipo “Implementation Constraints File”.

Generada

la nueva fuente, nos cargará el entorno PACE tal y como se aprecia en la foto.

Ahora

asignaremos los pines como Input/Output.

Generar archivo *.jed

Por último, antes de la programación del CDPL, crearemos el archivo *.jed

haciendo doble click en "implemente design".

Si todo ha salido correctamente nos aparecerán todas las partes con un tick

verde. En la ventana del editor de la derecha nos cargará un resumen con los

datos del proyecto.

Proceso descarga al Cpld

Como en los casos anteriores abriremos Impact y crearemos un nuevo proyecto.

A continuación configuramos el dispositivo utilizando Boundary-Scan(Jtag)

.

Una vez que nos haya cargado el entorno de Impact y se haya establecido la comunicación, abriremos el archivo rotativa.jed. Podemos realizar un borrado con la opción erase.

Finalizado el borrado, hacemos doble click en "Program" para iniciar la descarga

Como ya tenemos programado el Cpld, simplemente realizaremos el conexionado en la TAD que nos quedará de la siguiente forma según el archivo de restricciones generado. Debo añadir, que tuve que modificar el archivo de restricciones, asignando los pines 25 y 17 para el pulsador B y el F.carrera A, y el global clock en el pin 10.

Este es el resultado final...

Descarga aquí el programa

No hay comentarios:

Publicar un comentario